PCB 设计规则

嘉立创EDA支持在原理图中直接设置 PCB 设计规则及其他配置,并在转换为 PCB 时同步更新。

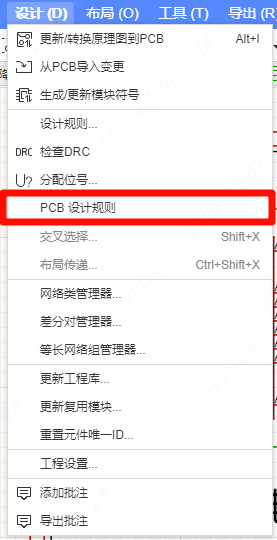

功能入口:

- 顶部菜单栏 - 设计 - PCB 设计规则

完整的 PCB 设计规则可以查看 PCB设计 - 设计规则

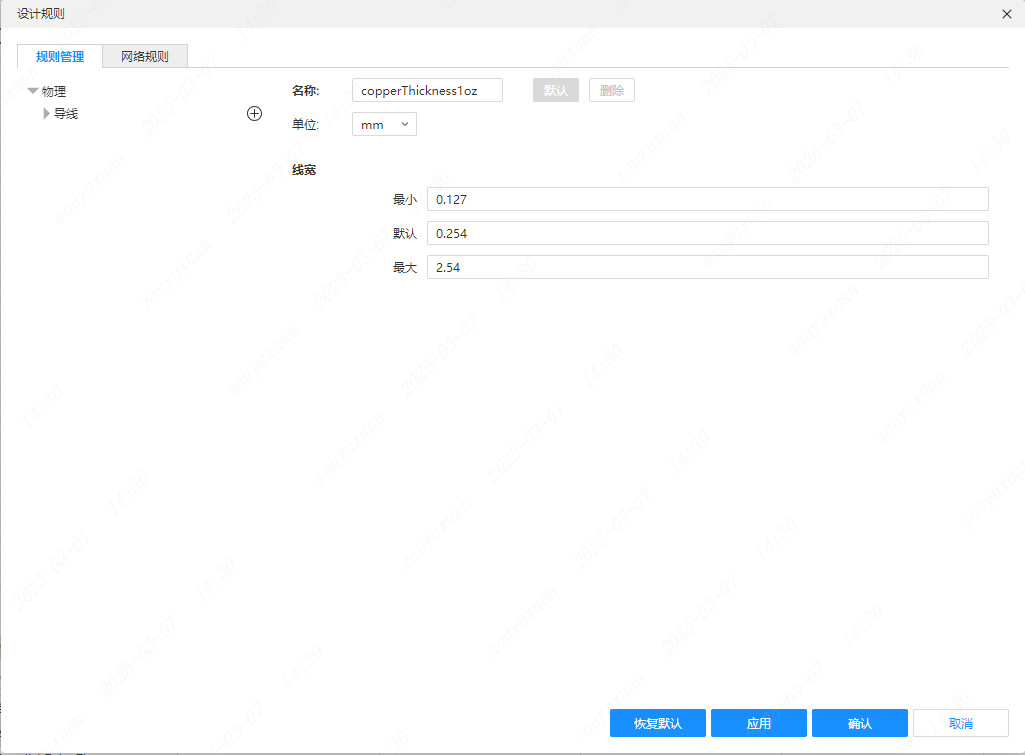

设计规则

在原理图中,用户可以设置转换后的 PCB 导线线宽规则,具体包括最小、默认和最大线宽的设定。转换后的 PCB 将依据这些规则进行 DRC(设计规则检查),以确保导线线宽符合要求。

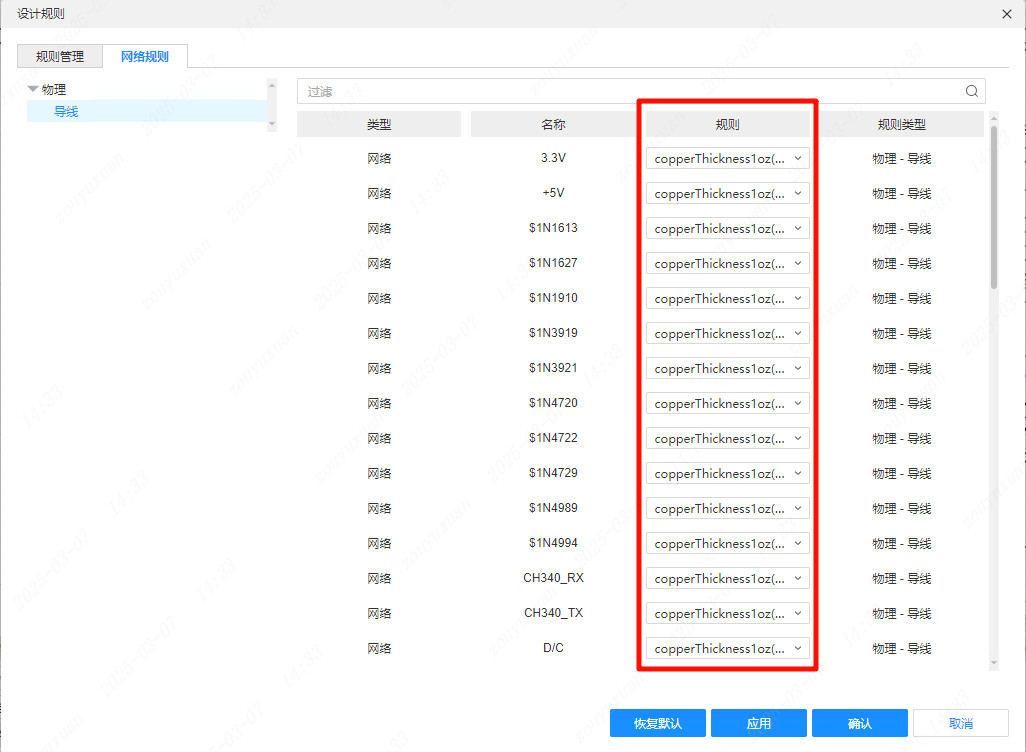

在网络规则中,用户可以为不同的网络配置特定规则。通过此功能,可以在原理图中为各导线网络分配相应的设计规则,确保转换后的 PCB 按照该规则进行设计。

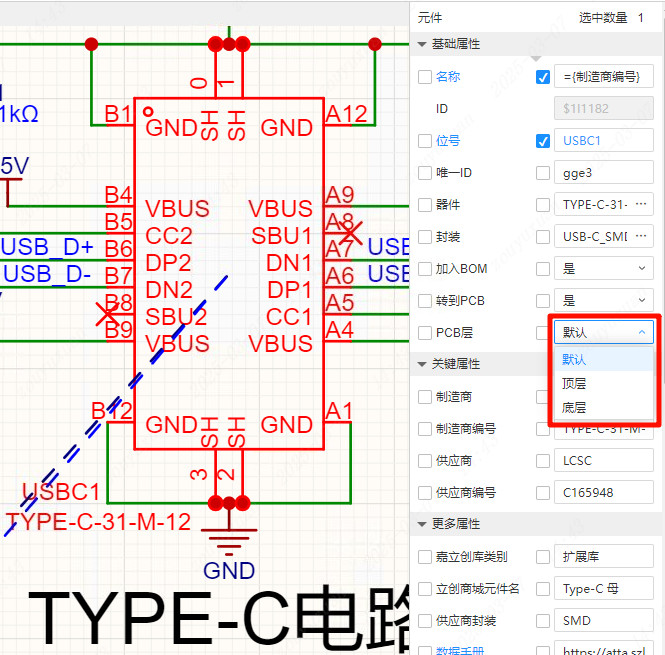

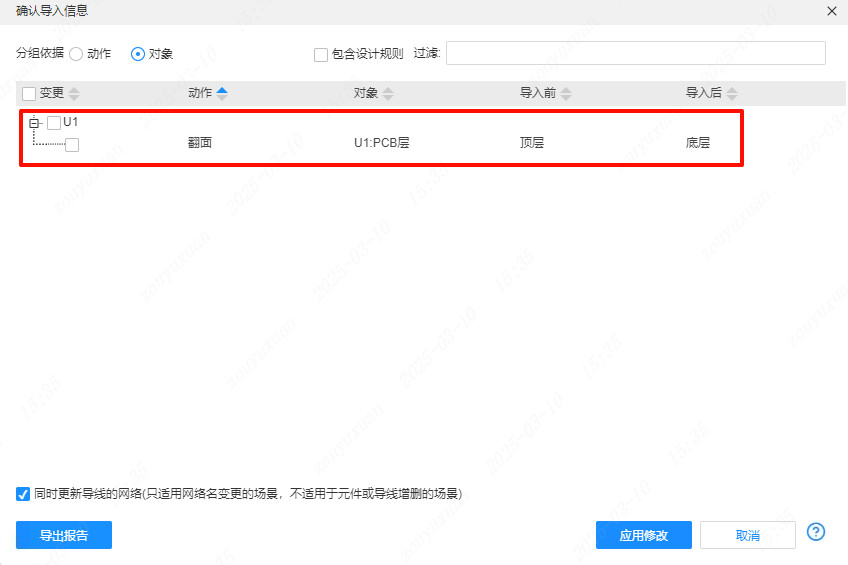

元件所在 PCB 层

支持设置元件在转换为 PCB 后的所在层。用户可以在原理图中配置元件的基础属性,以指定其对应的 PCB 层。

在原理图中修改元件所在层后,还需在导入PCB时,勾选发生变更的选项以确保更改生效。

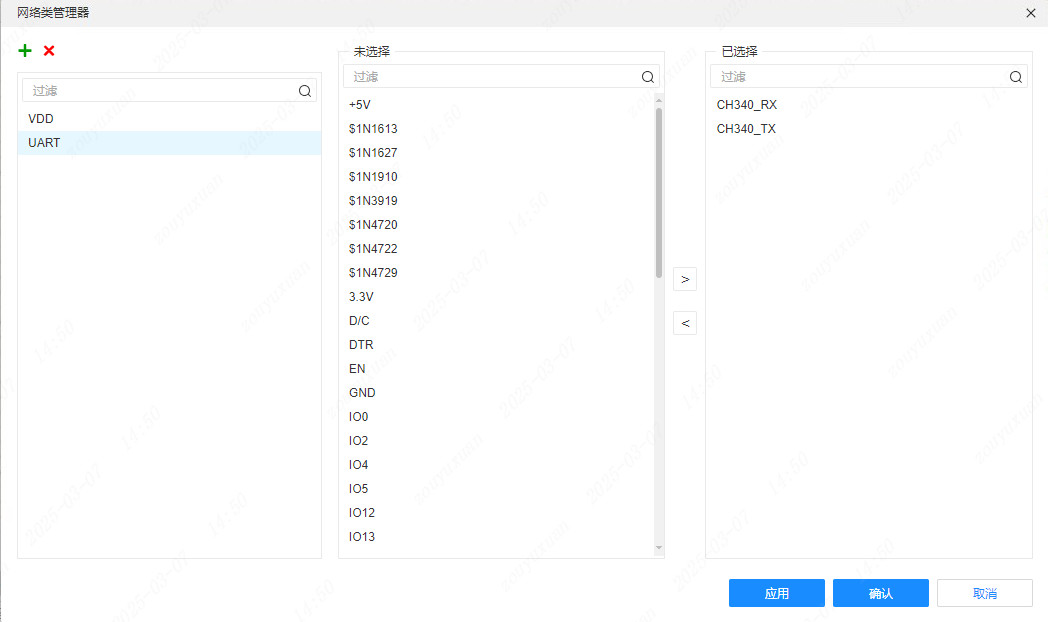

网络类管理器

功能入口:

- 顶部菜单栏 - 设计 - 网络类管理器

原理图中新增了与 PCB 设计相匹配的网络类管理器,便于在绘制 PCB 之前对网络进行分组管理。

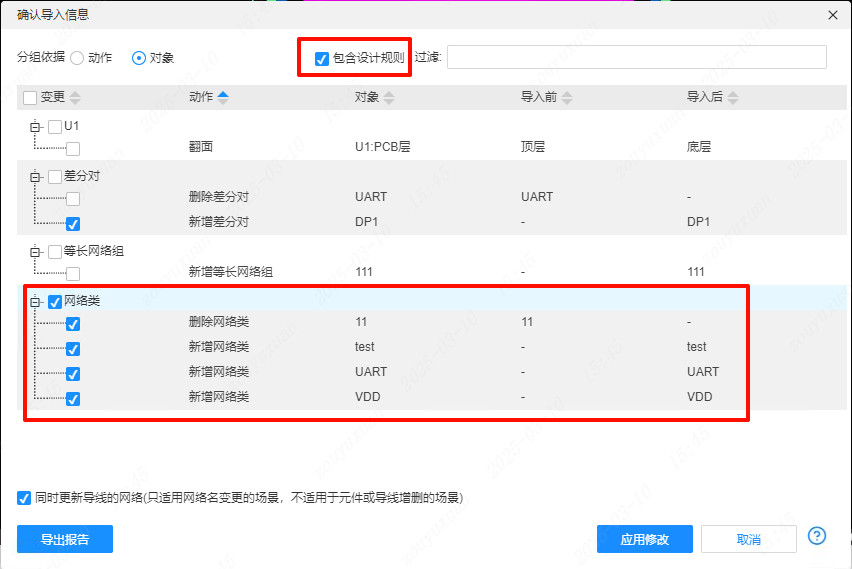

完成网络类配置后,通过点击设计 - 更新/转换原理图到PCB选项,在弹出的确认导入信息窗口中勾选包含设计规则,并在表格中选择需同步的设计规则,最后点击应用修改按钮,即可实现网络类信息从原理图向 PCB 的同步更新。

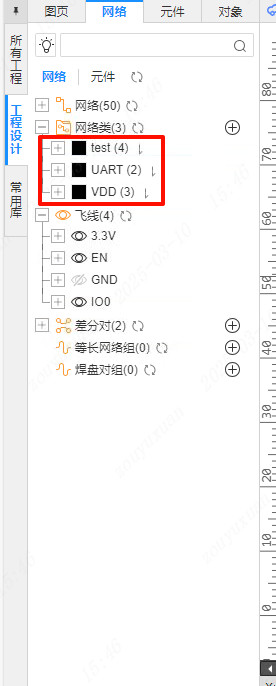

用户可以在左侧文档树的网络页面中查看网络类的同步状态。

差分对管理器

功能入口:

- 顶部菜单栏 - 设计 - 差分对管理器

原理图中新增了与 PCB 设计相匹配的差分对管理器,便于在绘制 PCB 之前定义差分对。

完成差分对配置后,通过点击设计 - 更新/转换原理图到PCB选项,在弹出的确认导入信息窗口中勾选包含设计规则,并在表格中选择需同步的设计规则,最后点击应用修改按钮,即可实现差分对信息从原理图向 PCB 的同步更新。

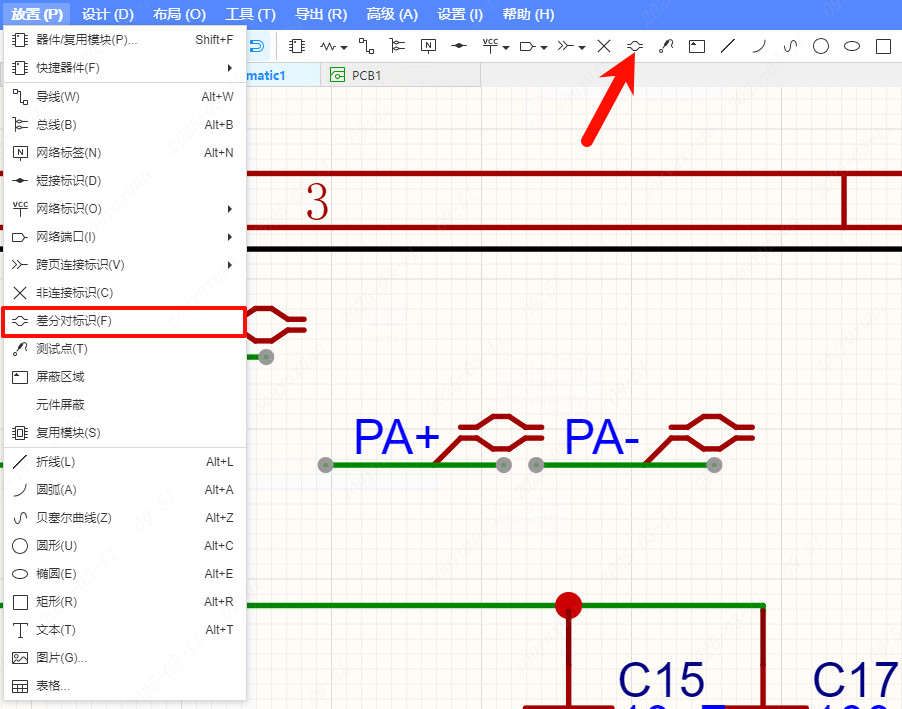

原理图中新增差分对标识,可在 放置 - 差分对标识 和顶部工具栏中调用。

放置了差分对标识的网络,可在差分对管理器中被快捷选择。

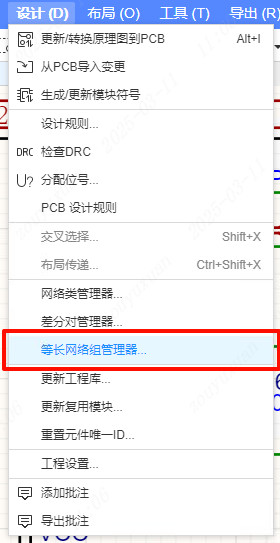

等长网络组管理器

功能入口:

- 顶部菜单栏 - 设计 - 等长网络组

原理图中新增了与 PCB 设计相匹配的等长网络组管理器,便于在绘制 PCB 之前定义等长网络组。

完成等长网络组配置后,通过点击设计 - 更新/转换原理图到PCB选项,在弹出的确认导入信息窗口中勾选包含设计规则,并在表格中选择需同步的设计规则,最后点击应用修改按钮,即可实现等长网络组信息从原理图向 PCB 的同步更新。